-

Notifications

You must be signed in to change notification settings - Fork 14

New issue

Have a question about this project? Sign up for a free GitHub account to open an issue and contact its maintainers and the community.

By clicking “Sign up for GitHub”, you agree to our terms of service and privacy statement. We’ll occasionally send you account related emails.

Already on GitHub? Sign in to your account

[LLVM 6.0] flt2dec / dec2flt cause assertion failed: Wrong topological sorting #101

Comments

|

/cc @brainlag |

|

Since I got my bugpoint setup working and fixed all my paths, I can now report a new cra-- oh. 😄 One piece of addition information: I did not apply #99 and I still got this crash in exactly the same place. |

|

I've been looking into this issue a bit (with a slightly different repro since I'm using a newer LLVM version). The issue appears to be that whatever data is passed to Note that this seems to be related to optimizations. Compiling with |

|

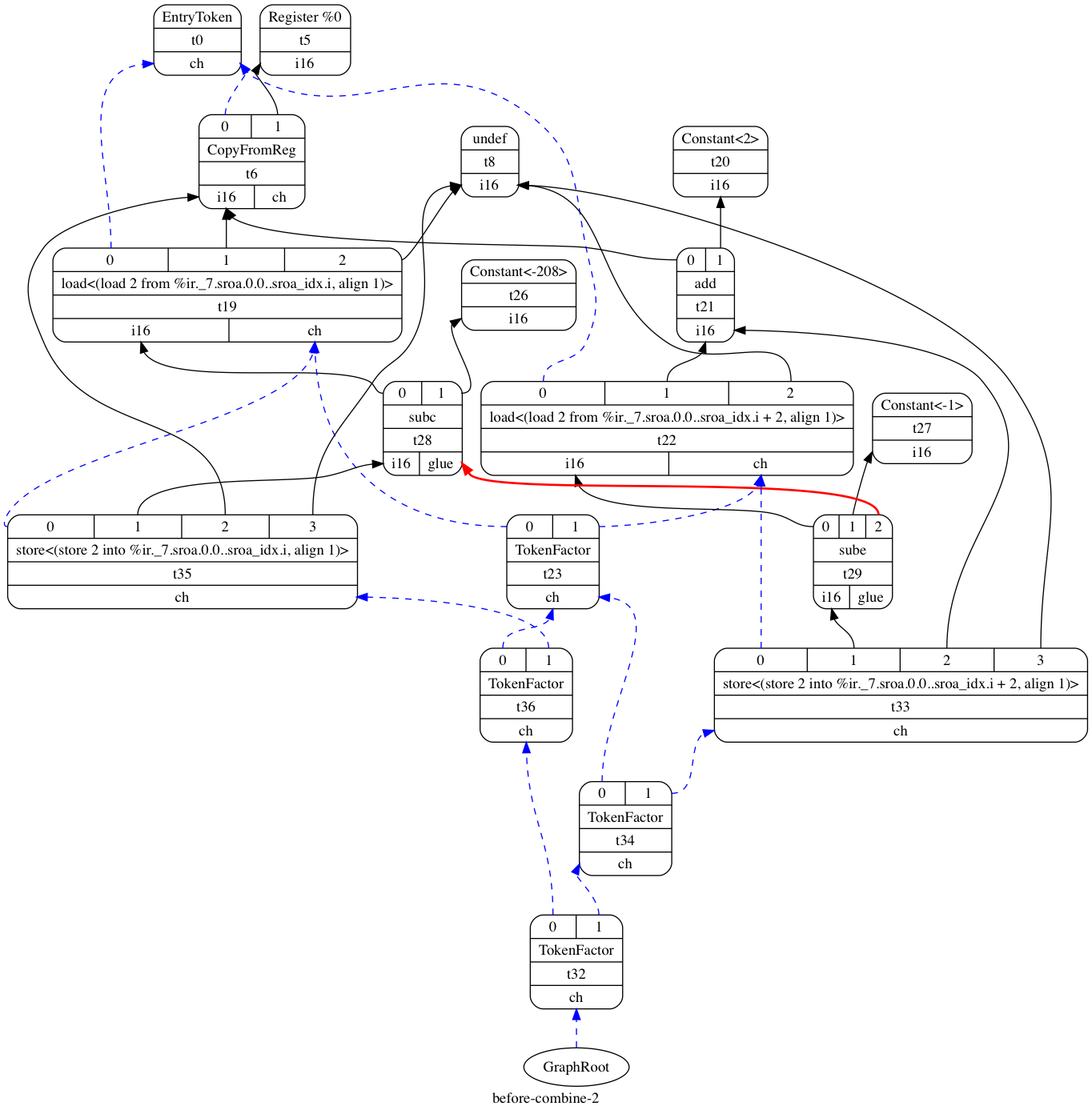

In case that helps anyone, here is what I believe is the relevant part of the The "LLVM ERROR: out of memory" seems easily explainable to me: LLVM apparently wants to compute the depth of the "DAG" for debug printing. Since the DAG contains a cycle, we get an infinite loop. |

|

If you compile llvm with asserts you will hit that and don't run into OOM error. |

|

There are glue nodes which glues 2 (or more?) nodes together |

|

Ah, I wasn't aware that "glue nodes" are an LLVM concept. Anyway, I think I understand now what you meant and see it for my example as well. So, IIUC, the next step would probably be figuring out why the two nodes are glued together. In any case, I'm including the relevant graphs below, in case they are useful to anyone: |

|

I think I know now what happens: In This may only be done if

The check for "!Op->isPredecessorOf(N) && !N->isPredecessorOf(Op)" then "correctly" identifies that they are independent, if one considers only the edges actually present in the graph. The issue now is that the glue link between I can see three solutions to this:

Intuitively, I don't think that (1) is feasible and don't like (3) as a solution. I'll try to figure out why / how / where the glue is inserted in the first place. Edit: Any thoughts on the three proposed solutions? |

|

The glue nodes are generated by LLVM in |

|

Imho, and i might be wrong, this is flaw in llvm. Either way I think you should discuss this with the llvm developers. Also, when I looked up the code for |

|

Yeah, I think you are correct that this can be considered an LLVM bug. I'll write to the mailing list or open a bug tomorrow.

That commit should be a non-functional change. It just ensures that |

|

llvm-dev thread (or rather, initial message): http://lists.llvm.org/pipermail/llvm-dev/2018-October/126851.html |

|

Per the first reply on the ML, I've tried to disable the I don't know yet if that breaks something else. Worstcase, I hope that this only makes things slower, which could be fixed by adding support for the Live-Edit: I've just ran the AVR CodeGen tests and took a closer look at |

|

And someone has a proposed fix for the glue |

|

We've recently upgraded to LLVM 8 🎉 I'm going to close any bug that is reported against an older version of LLVM. If you are still having this issue with the LLVM-8 based code, please ping me and I can reopen the issue! |

|

@shepmaster: This has a not-yet-upstreamed patch on the 8.0 branch, so I think we should keep the issue open? |

|

Built the official 8.0 release code with AVR target enabled, llced the code in OP, and it seems |

|

The way forward here is to convert the AVR backend from the old https://reviews.llvm.org/D53106#1443059

|

|

Hm, I can't reproduce this on LLVM trunk anymore, on either testcase. ; ModuleID = 'bugpoint-reduced-simplified.bc'

source_filename = "bugpoint-output-95356ba.bc"

target datalayout = "e-p:16:8-i8:8-i16:8-i32:8-i64:8-f32:8-f64:8-n8-a:8"

target triple = "avr-unknown-unknown"

%"num::bignum::Big32x40" = type { [0 x i8], i16, [0 x i8], [40 x i32], [0 x i8] }

; Function Attrs: uwtable

define void @"core::num::dec2flt::num::digits_to_big"() unnamed_addr {

start:

%_7.sroa.0.0..sroa_idx.i = getelementptr inbounds %"num::bignum::Big32x40", %"num::bignum::Big32x40"* undef, i16 0, i32 3, i16 0

switch i2 undef, label %bb5.i10 [

i2 0, label %bb2.i

i2 1, label %bb3.i

i2 -2, label %bb4.i

]

bb2.i: ; preds = %start

ret void

bb3.i: ; preds = %start

%0 = add i8 0, -48

%1 = zext i8 %0 to i32

%2 = load i32, i32* %_7.sroa.0.0..sroa_idx.i, align 1

%3 = call { i32, i1 } @llvm.uadd.with.overflow.i32(i32 %2, i32 %1)

%4 = extractvalue { i32, i1 } %3, 0

store i32 %4, i32* %_7.sroa.0.0..sroa_idx.i, align 1

unreachable

bb4.i: ; preds = %start

unreachable

bb5.i10: ; preds = %start

unreachable

}

; Function Attrs: nounwind readnone speculatable

declare { i32, i1 } @llvm.uadd.with.overflow.i32(i32, i32)Using avr-rust at

|

|

I cherry-picked avr-rust/llvm-project@56d676b and avr-rust/llvm-project@a5b6478 into the |

(cherry picked from commit 626f49c)

This is with my recently-rebased branch based on upstream Rust 190a6c. I've added the patch from #99 locally.

Case 1

Case 2

Error

The text was updated successfully, but these errors were encountered: